NANO: Brief Reports and Reviews Vol. 15, No. 11 (2020) 2030005 (15 pages) © World Scientific Publishing Company DOI: 10.1142/S1793292020300054

## Memristors: Understanding, Utilization and Upgradation for Neuromorphic Computing

Mohanbabu Bharathi\*, Zhiwei Wang\*, Bingrui Guo<sup>†</sup>, Babu Balraj<sup>‡</sup>,

Qiuhong Li<sup>§</sup>, Jianwei Shuai and Donghui Guo,\*,\*\*

\*Department of Electronic Engineering

Xiamen University, Xiamen 361005, P. R. China

<sup>†</sup>Department of Applied Mathematics

Computer Science, University of California, San Diego USA

<sup>‡</sup>Department of Physics, NCHU University

Taichung City 402, Taiwan

<sup>§</sup>Pen-Tung Sah Institute of Micro-Nano Science

and Technology Xiamen 361005, P. R. China

<sup>¶</sup>Department of Physics, Xiamen University

Xiamen 361005, P. R. China

<sup>|</sup>mohanbabu@xmu.edu.cn

\*\*dhquo@@xmu.edu.cn

Received 6 July 2020 Accepted 28 September 2020 Published 12 November 2020

The next generation of artificial intelligence systems is generally governed by a new electronic element called memristor. Memristor-based computational system is responsible for confronting memory wall issues in conventional system architecture in the big data era. Complementary Metal Oxide Semiconductor (CMOS) compatibility, nonvolatility and scalability are the important properties of memristor for designing such computing architecture. However, some of the concerns, such as analogue switching and stochasticity, need to be addressed for the use of memristor in novel architecture. Here, we reviewed a number of important scientific works on memristor materials, electrical performance and their integration. In addition, strategies to address the challenges of memristor integration in neuromorphic computing are also being investigated.

Keywords: Memristor; von Neumann architecture; neuromorphic computing; synapse plasticity; in-memory computing.

#### 1. Introduction

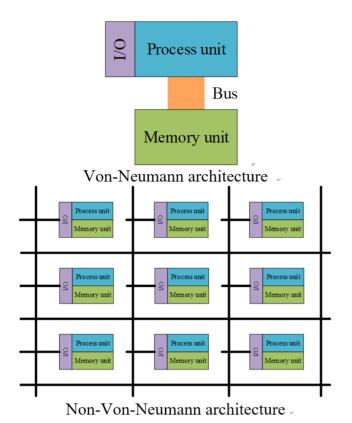

Contemporary computing systems are unable to address the critical challenges of size reduction and computing speed in the Big Data era. However, the same conventional systems are generally used for day-to-day activities such as document preparation, streaming audio and video and playing games. These systems are essentially designed on the basis of the von Neumann architecture method

and reformed in such a way that computers are convenient to use for general purposes. However, the restructured systems are highly incompetent for intensive information processing. The von Neumann bottleneck<sup>2</sup> is referred to as a hindrance in data transfer through the bus connecting processor and memory cell. Conversely, the memory wall limitation of the von Neumann machine is highly motivating recent research activities on alternative

<sup>\*\*</sup>Corresponding author.

computing architectures. This gives an opportunity to create alternative architectures based on a biological neuron model. Neuromorphic computing<sup>3</sup> is one of such alternative architectures that mimic neurobiological brain architectures as a way out of the von Neumann bottleneck.

The humanoid neural brain system comprises approximately 100 billion neurons and numerous synapses of connectivity.<sup>4</sup> An efficient circuit device is therefore essential for the construction of a neural network that mimics the human brain. Williams' demonstration of the new memristor element in his workroom gave rise to new possibilities for hardware implementation in alternative architecture.<sup>5</sup> The development of memristor, with several distinctive features such as scalability, in-memory processing and CMOS compatibility, significantly facilitated the implementation of neural network hardware.<sup>6-9</sup> The basic electrical component memristor, which is a two-terminal component, works as a nonlinear resistor property along with the memory function.<sup>10</sup> Memristor is a capable electronic component to find applications especially for memory devices, logical circuitry networks and neuromorphic systems. The ability to memorize the current and current direction can be used effectively to reduce the size of the device and increase the processing speed in neural networks. In addition, the memristor is used to manufacture memory cells in the same processing unit chip in the neural network. As in the cerebral nervous system, parallel calculations are made with the support of memristor devices in a novel computing architecture.

This paper is presented as follows: Sec. 2 begins with the notion of a memristor and its properties. Neuromorphic computing is concisely discussed in Sec. 3. Section 4 contributes to the various significant behaviors of memristors in neuromorphic applications. The challenges of integrating memristor into neuromorphic computing are outlined in Sec. 5 with promising strategies for augmenting the network system. Suggestions for improved performance of memristor devices have been illustrated in Sec. 6. Finally, Sec. 7 explores the possibility of harnessing the properties of memristor devices to achieve a rapid computing system, such as a biological computing method.

#### 2. Memristor

The memristor was introduced as a "memory-like resistor" where the background of the applied

Fig. 1. Symbol of memristor.

inputs (voltage or current) would alter the resistance status of the device. Various curves of the input applied produce a different dynamic response and final resistance.<sup>7</sup> In addition, if the input is removed for some time, the device will restart the operation from the last resistance state from where it is left. In addition, the memristors often react to the current direction, i.e., polarity. The memristor symbol in the electronic diagrams as in Fig. 1 clearly shows this polarity in the device. The interrelation between response behavior and nonvolatility of the system determines its usability as a storage device or as a neuromorphic computer.<sup>9</sup>

A memristor, which is a passive component, works like a nonlinear memory resistor. The fourth key element memristor after resistor, capacitor and inductor was theoretically anticipated in 1971. However, scientists in HP labs have demonstrated the fabrication of devices with electronic properties such as this memristor device. He novel electronic component is called memristor because it is associated with both the resistor and the memory function. The memory of past resistance history is the most elementary function of this memresistance device. The resistive switching mechanism raises the application of the memristor device to neuromorphic computing.

The following list of new and established companies is more involved in emerging device technology for memristors. Companies that we know include Intel, Samsung, HP, IBM, IMEC, Fujitsu, SMIC, Sharp, TSMC, NEC, Panasonic, Macromix, Crossbar Inc., Qimonda, Ovonyx, KnowM, 4DS Memories Ltd., Global Foundaries, Western Digital (previously called SanDisk), Toshiba, Macronix, Nanya, NEC, Rambus, ST Microelectronics, Winbond, Adesto Technologies Corporation, HRL Laboratories LLC and Elpida. This memory device allows the storage of data with low resistance for Boolean 1 and high resistance for Boolean 0. Resistance switching from high to low is represented by SET operation and RESET operation is considered

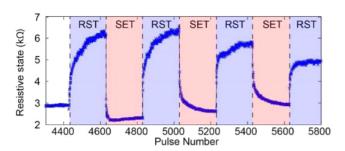

Fig. 2. SET and RESET operation of TiO<sub>2</sub> memristor. <sup>12</sup>

to be a transition from LRS to HRS. Figure  $2^{12}$  depicts the SET and RESET operation of the  $\mathrm{TiO}_2$  memristor for a clearer understanding of the operation. Deep knowledge of the properties of memristor is a prerequisite for exploring many physical mechanisms of device fabrication.

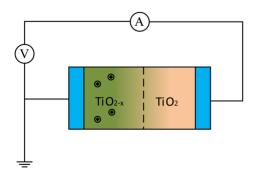

The memristor, as demonstrated by HP Lab,  $^{11}$  is a structure-like capacitance. The bilayer dielectric titanium dioxide material is layered between two platinum electrodes, as shown in Fig. 3. The bilayer consists of doped  $\mathrm{TiO}_{2-x}$  and undoped  $\mathrm{TiO}_2$ . The doped  $\mathrm{TiO}_2$  layer has more positively charged ions with oxygen vacancy. Thus, two different regions of resistance are formed. The external voltage bias is used to modify the region's resistance. Oxygen vacancy moves accordingly with the applied electrical field, which at the same time shifts the boundary between low and high resistance.  $^{13}$

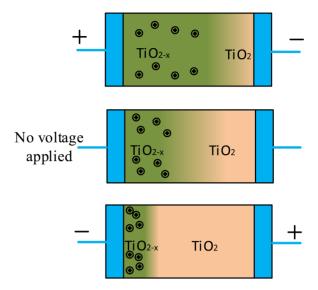

The applied positive signal voltage moves oxygen vacancy from the doped oxide region to the undoped oxide region. As a result, the width of the insulating layer decreases. Consequently, the conductivity of the entire switch increases as shown in Fig. 4.<sup>13</sup> The conductivity of the device depends on the positive voltage applied whereas the negative signal attracts oxygen vacancy and the insulating layer widens. The increased width of the insulating layer makes the device less conductive. If

Fig. 3. Biased circuit of memristor.

Fig. 4. Movement of boundary for different biasing voltages.  $^{13}$

the input signal is switched off, the boundary is stationary due to no migration of vacancies. The conductance/resistance of the device is therefore constant. Thus, memristor remembers the voltage applied or its resistance.

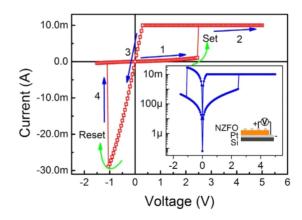

After restarting the charge flow in the circuit, the memresistance begins to change. These characteristics need to be discussed more clearly in order to understand the memristor device. Multistate resistance properties are therefore commonly understood by studying the characteristic curve of I-V. The I-V study is performed by applying voltage sweeps between positive and negative signals. The memory resistive switching of NiZn was studied by Wu et al. Figure 5 shows the properties of the NiZn memristor. The important properties of resistance in the device vary from low resistance to high resistance and high to low resistance to

Fig. 5. Characteristic curve of NiZn memristor. 14

applied continuous voltage sweeps. As a result, the device exhibits different resistance behaviors. The device was in ON condition until the applied voltage reached 5 V. This formation is also referred to as "set" action. The "reset" action occurred with the backward voltage sweep from 5 V to 0 V. As a result, the data can be stored, read and restored by applying voltage/current pulses to the device. This switching action is essential for the synapse emulator in neuromorphic applications.

Generally, metal–insulator–metal stacked structure is used for the design of a memristor device similar to the structure used by the HP lab.<sup>5</sup> The memristor can be made of any combination of metals and insulators. The insulating layer is the most important material for the memristor. The insulating material has important properties such as switching mechanism, resistance ratio, working voltage polarity and working speed. A lot of insulators and semiconductors could be used as an insulating layer. A lot of metals, alloys and semiconductors are used as electrodes. The electrodes are carefully selected as they significantly affect the performance of the memristor device.

Numerous studies have been conducted on NiO dielectric material for the fabrication of resistive switching devices. <sup>15</sup> NiO-based memoristors have a large SET/RESET ratio and unipolar switching properties. However, they are not appropriate for reducing power consumption as high current is needed for RESET operation. However, another material  $Al_2O_3$  is widely used for power efficiency. <sup>16</sup> The unique optical properties of ZnO facilitate the fabrication of transparent substrates in memristor devices. <sup>17,18</sup> Wang et al. successfully fabricated a memristor based on  $MoS_{2-x}O_x$  with graphene as an electrode for flexible electronic applications. <sup>19</sup> Memristor devices based on CuO and SiO<sub>2</sub> are good for CMOS compatibility. <sup>20</sup>

### 3. Types of Memristors

Since the emergence of the memristor theoretical concept and experimental evidence of memristor, various types of memristor devices have recently been reported. Most memristor devices are included in redox-based random-access memory (ReRAM), magneto-resistance RAM (MRAM), phase-change RAM (PRAM) and ferroelectric RAM (FeRAM) types. Each of these memristors has special advantages and disadvantages, respectively. These memory devices have been mainly used in memory

equipment due to their nonvolatility, high speed, higher density and reliability properties as well.<sup>21–24</sup>

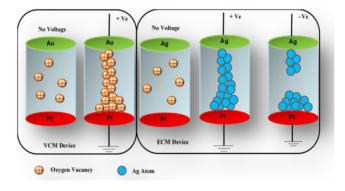

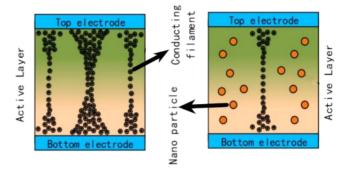

#### 3.1. ReRAM

ReRAMs usually operate under nanoionic systems and have a structure like metal-isolator-metal. Such devices operate under both the ion motion and the redox reaction mechanism.<sup>25</sup> These device mechanisms have been detected in different materials, e.g., metal oxides, chalcogenides, nitrides and organic materials.<sup>26–28</sup> The advantage of ion motion under external field is that ions have a much higher mass than electrons and are therefore electronically resistant to other noises and more stable. ReRAM equipment is fabricated by sandwiching the active material between two metal electrodes. In general, ReRAM devices can be categorized as Valance Change Memory (VCM) and Electrochemical Metallization Memory (ECM) for the ReRAM operating mechanism. The difference is that the conductivity changes in the active layer of the device are subject to the movement of oxygen vacancy in VCM as well as metal-based cation movements in ECM devices. The migration of oxygen and metal ion vacancy in the active layer is shown in Fig. 6.

For VCM memristors, the active material generally consists of metal, metallic complex and non-metallic oxides. In such devices, the conductive filament is formed or annihilated by electrical field effect and thermal effect. The structural defects of the active material cause oxygen vacancy in the layer. Oxygen ion and positively charged oxygen vacancy causes the active layer to migrate easily. Such migration of ions causes the filaments to be formed in the active layer and thus the device shows the characterization of the memristor. With regard

Fig. 6. Switching mechanism of VCM- and ECM- based memristor devices.

to nonmetal oxides, SiO<sub>2</sub> is one of the most important active materials for memoristors due to its exceptional CMOS compatibility. Kim et al. have successfully fabricated a ReRAM crossbar configuration memristor device.<sup>29</sup> Al<sub>2</sub>O<sub>3</sub> is another widely used dielectric material. This is usually used to combine Al<sub>2</sub>O<sub>3</sub> with a different switching layer to reduce system current in low-current applications. Kai et al. introduced the Al<sub>2</sub>O<sub>3</sub> active layer together with InGaZnO to reduce the complaint current from the milliampere scale to the microampere scale.<sup>30</sup> The resistive switching mechanism of the VCM device can also be discussed with ECM. In the first place, oxygen ions are considered solely responsible for the resistive switching mechanism in memristor devices.<sup>31</sup> However, the recent research work confirms that metal cations also participate in the filament formation in ECM device structure.<sup>32</sup>

Such ECM devices are also referred to as RAM for solid electrolyte or conductor bridging. Metal cations in ECM systems are responsible for variations in resistance between the two electrodes in the active layer. They are believed to be mobile species in ECM devices. The metal cations of the electrode are movable through the solid active material and modify the conductivity. Occasionally, metal cations may originate from the doped metal ion in the active material. Zhuge et al. studied metal conducting filament growth in the active layer in the memristor device based on ECM.<sup>33</sup> The Cu filament's rupture and rejuvenation occurred in the active material. In addition, doping atoms have also had an impact on memristor performance.<sup>34</sup>

# 3.2. Spintronic and magnetic memristors

In addition to redox-based memristors, spin-based memristors offer advantages over other memristors with endurance, high density and energy efficiency for nonvolatile memory devices and bio-inspired computing applications. Zhang et al. demonstrated a magnetic memristor device using a spin-orbit torque.<sup>35</sup> The domain wall is continuously drifted forward and backward inside the active layer by applying positive and negative current pulses. This result paved the way for the development of an energy-efficient memristor for neuromorphic computing. Perovskite material has characteristics such as massive magnetoresistance, spinal orbit load order, spinal polarization and electrical phase separation. They are therefore recently attracted to

the fabrication of magnetic memristor.<sup>36</sup> Chen and Wang demonstrated the magnetic memristor function by shifting the spin torque.<sup>37</sup> The resistance of the device changes according to the magnetization of the device by varying the current applied. In addition, biosynapses with more than 1000 stable endurance is also shown in the magnetic memristor.<sup>38</sup> Recent developments in the field of magnetic nanowire wall motion have made memristor devices more reliable in the field of neuromorphic computing. A short pulse of spin-polarized current is used to move the domain wall to write and read memory.<sup>39</sup> Thus, spintronic and magnetic memristors have the potential to mimic biosynapses for brain-inspired computing applications.

### 3.3. Phase change memristors

In addition to these types of materials, memristor devices are fabricated using phase change materials. Phase change memristors also work as redox memristor by changing resistance states by applying current pulse or threshold temperature. The resistance of the materials is altered by altering its structure between the ordered crystalline and the unordered amorphous. 40,41 Chalcogenide materials are generally used for this type of phase change memristor devices. The most common chalcogenide material Ge2Sb2Te5 is widely used to manipulate the memristor properties of phase change material.<sup>42</sup> However, the phase change memristor also has many challenges for practical applications. The speed of resistance switching in this type of memristor is very slow. And also, the high programming current used to reset the device is one of the other typical challenges of phase change type memoristors. 43,44 In addition, nanostructured thermal electrical system circuits for encryption, non-Boolean computing and bio-inspired neural network computing are rendered using the  $VO_2$  phase change memristor.

In addition, ferroelectric material is one of the other materials which can be used for the fabrication of memristor devices. The polarization of such materials is modified to achieve resistance switching properties by varying the input voltage. Therefore, the list of advantages in working with memristor includes high resistance switching relationship, analogue memory type, long retention time and long endurance cycles. Memristors may also be used instead of selector devices. Memristor is therefore well thought out beyond the architectural systems of von Neumann. 47,48

### 4. Neuromorphic Computing

Conventional von Neumann architectural systems are the backbone of our day-to-day activities, such as document preparation, streaming audio and video and playing games. But these systems are difficult to calculate complex inputs and outputs. The systems are therefore to be reformed in a manner similar to human intelligence for learning and problem solving by processing a large amount of data.<sup>49</sup> These artificial intelligence (AI) systems are well developed and continue to evolve stage by stage. The first generation of AI was overtaken by conventional decision making in a specific problem area. AI of the second generation is generally concerned with sensing and perception using deep-learning networks. This type of AI is currently used in almost every location. In addition, contemporary von Neumann computing systems are unable to address the critical challenges of size reduction and computing speed in the Big Data era.<sup>50</sup> In order to overcome these limitations, the next forthcoming AI will be extended to the areas of interpretation and autonomous adaptation, such as human cognizance. Neuromorphic computing is concerned with emulating the probabilistic computing, the neural structure and the functioning of the human brain. Human brain function is therefore mainly motivating to achieve efficient AI technology computing. New generation AI is now developing algorithmic solutions to address current instability, inconsistency and uncertainty.

Mead<sup>51</sup> proposed the term neuromorphic to indicate analog circuits capable of imitating bioneural behavior. The field has seen an exponential growth in the creation of new neuromorphic architectures that can mimic the activity of certain parts of the brain neuron network in recent years. Memristors, whose behavior is similar to the neuron, are commonly used in the neuromorphic computing system. Approximately 100 billion neurons and numerous synapses of connectivity make human brains more complex in nature.<sup>52</sup> Even though the modern computers work efficiently, they cannot be matched to neural network.

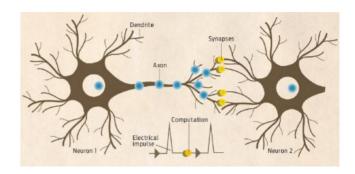

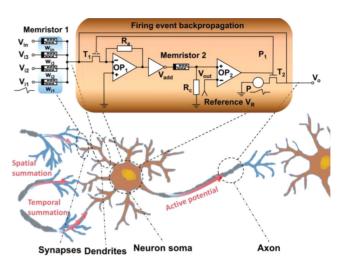

A biological neuron cell sometimes consists of a cell body, an axon and dendrites. The information is transmitted from the axon to the dendrites by the synapse process as shown in Fig. 7. Information is passed through the neuron by changing the voltage potential of the neuron and thus affects the load on other neurons.<sup>53</sup> The word "fire" expresses

Fig. 7. The synapse between two bological neurons.<sup>31</sup>

the threshold potential of the neuron and is ready to alter the next one. In particular, the fired spike (potential change) is also transmitted in reverse to the presynaptic neurons for weight adjustment.<sup>54</sup> The same concept of accumulation charge to fire other neuron potential is realized in most neuron models in neuromorphic systems.

The conductance of the synapse (i.e., synaptic weight) regulates the activities of the pre-and post-synaptic neurons. Synapse function is the most important element in neural networking systems. Optimization of synapse implementation is more critical to the development of new materials in a new computing system. The synaptic plasticity mechanism is the reason for the synaptic weight change. Synaptic plasticity is primarily responsible for the neuron learning process in the system.

Neuromorphic systems use the biological neuron system to invalidate the von Neumann bottleneck by means of massive parallel connectivity. <sup>57,58</sup> In the von Neumann architecture resulting in the von Neumann bottleneck, the processor and the memory are separate. But the Big Data era expects faster computing at the same location. Memory and synapses are therefore placed together in the case of neuromorphic architecture (as shown in Fig. 8) to ease the problem of the bottleneck. It is worth noting that the neuromorphic computational architecture does not replace conventional architecture, but complements the von Neumann architecture to handle large data processing.

As a result, scientists are motivated to work on a variety of divisional aspects of process and architecture to match brain-like function. <sup>59</sup> Nowadays, synapses of artificial neural networks (ANNs) are still designed using a lot of digital complementary metal—oxide—semiconductor (CMOS) devices at atomic level. <sup>60,61</sup> However, these devices are not really capable of simulating the behavior of

Fig. 8. Von-Neumann and neuromorphic computing architecture.  $^{36}$

biological synapses. As a result, energy consumption is also extremely high. Surprisingly, various device resistance materials are being studied to simulate the synapse function.  $^{62-64}$  Although the key functionalities of the neural networks are achieved by these emerging technologies, there are still major obstacles to the success of the new computer system.

#### 5. Memristor Neuron

Biological neural systems are replicated in order to exploit the advantages of the human brain for neuromorphic computing. Electronic neurons are fabricated using a number of electronic transistor devices. However, a novel memristor device is then proposed to mimic the biological neuron in order to simplify the circuit elements and the size. Al-Shedivat *et al.* demonstrated stochastic neurons using memristors. They used memristor resistive switching properties to imitate neuromorphic neural soma to integrate synaptic input and signal generation. The schematic diagram for the comparison of biosynapses and memristor-based synapses is shown in Fig. 9. The information is transmitted and processed in the neuron by updating its

Fig. 9. Architechture of memristor crossbar array.<sup>54</sup>

weight. The same can be modified by varying the resistance of the memristor devices. It is therefore easier to update the weight in circuit configuration of the memristor. In addition to other elementary circuit synapses, the precision of the learning process is enhanced by a strong connexion.<sup>67</sup> Linearity, multilevel and nonvolatility are key challenges in imitating memristor biosynapses. However, many researchers have made efforts to improve the analog memory characteristics of memristor for neuromorphic computing.

The nanoscale phase change memristor device was used to model an artificial neuron based on biosynapses by emulating a phase configuration similar to biomembrane potential variation.<sup>68</sup> In nanoscale phase change memristor works, the temporal integration of synaptic potentials is achieved by taking advantage of the structural reversal from the amorphous to the crystal structure in less time difference. The pulse output was obtained from the integration and fire neuron model by designing a circuit with memristor instead of a transistor. Synapses on weight handling challenges, including programmability and nonvolatile weight storage, are addressed by memristor bridge synapse. <sup>69</sup> Due to its multilevel synaptic weight adjustment, the memristor device can also be used to manipulate both input and output neuron signals. Mehonic and Kenyon have demonstrated a method for simulating synapse spiking using redox-based SiO<sub>2</sub> ReRAM.<sup>70</sup> The perfect memristor-based neuron has not yet been developed and commercialized. As a result, the field of memristor has become a focal point in device research to improve the properties of synapses to accommodate real biosynapses.

# 6. Memristor in Neuromorphic Computing

The conventional system is typically constructed by simulating human brains in the sequential function of the central processing unit.<sup>71</sup> In-memory computing, on the other hand, is a more revolutionary platform in the neural network. This revolutionary computing needs to be realized in a multiple analog resistive state in the memristor device. Such a computing system requires to resolve the memory wall bottleneck of the conventional system.<sup>72</sup> This memory wall consumes more data transaction energy. However, in-memory computing technology-based memristor is capable of overcoming the memory wall constraint as data is stored in the same processing location.

Many transistors are needed for the construction of a neuron model to mimic a biological neural system in conventional CMOS technology. However, CMOS devices can be replaced by memristor harnessing on the network. Al-Shedivat *et al.* showed neural spikes with the help of memristor.<sup>73</sup> Similarly, the analog modular neuron-based memristor is designed by Shamsi *et al.*<sup>74</sup> Pantazi *et al.* reported the use of phase change memristors for the emulation of neurons and synaptic plasticity.<sup>75</sup>

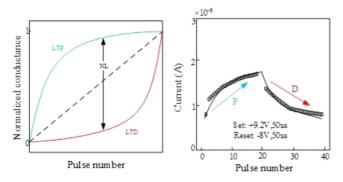

It is necessary to use the memristor in the network circuit for analog resistance behavior. The behavior of the external stimulus is analyzed to understand the behavior of the resistance. This behavior of the  $TE/HfO_x/AlO_x/BE$  memristor device is illustrated Fig.  $10.^{76}$  Conductivity with cycle number curves is also necessary to understand memristor. The abrupt change in conductance occurs initially, and the conductance of the saturation is gently attained. Thus, the conductance value either increases or decreases. This behavioral change in memristor can be compared with the

Fig. 10. Conductance characteristic curve of memristor device. <sup>49</sup>

Fig. 11. Architechture of memristor crossbar array. 54

same characteristics of biosynapses. The increase in conductance is called potentiation and the decrease in conductance is called depression.  $^{77-80}$

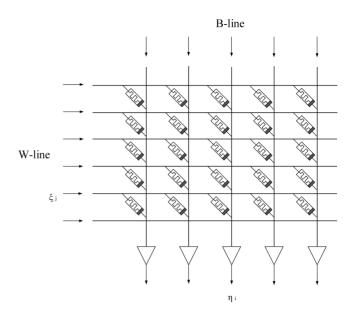

Memristive crossbar arrays are often used in ANNs to encode synaptic weights of synapse. The crossbar array network is shown in Fig. 11. The horizontal series of w-lines is connected by memristor through each junction.<sup>81</sup> In order to operate crossbar arrays, a potential signal is applied to a horizontal line and a vertical line is applied with a different voltage. The resistance of this connexon to the memristor is controlled by the possible difference between the voltages applied. 82 Crossbar arrays may be used for matrix-vector multiplication with the voltages used as inputs and outputs. Multilevel resistance allows the multiplication of the memristors of the matrix. However, memristors in ANNs are suitable for chip learning supervision. The input of the neuron in a given layer is calculated by multiplying the outputs of the previous neuronal layer in the ANN. Further, the memories used by traditional ANNs are ineffective with regard to energy usage during ANN processing because vector-matrix multiplication cannot be implemented directly in crossbar array structure. But the crossbar array of memristors has shown its dominance in terms of energy efficiency improvement. Crossbar memristor array can measure the matrix multiplication with a single sampling step for ANN circuit.

The crossbar array  $16 \times 16$  has been manufactured without any additional selector and Choi *et al.*<sup>83</sup> has demonstrated its self-rectification

function. Huh et al. used 2D material to make a synapse device to perform a memristor's neuro-modulator function.<sup>84</sup> Memristor is generally used for potentiation and plasticity of depression. Ham et al.<sup>85</sup> have demonstrated a new method of synapse production using photonics. Photonic synapses can improve efficiency and speed in the architecture of neural computing.

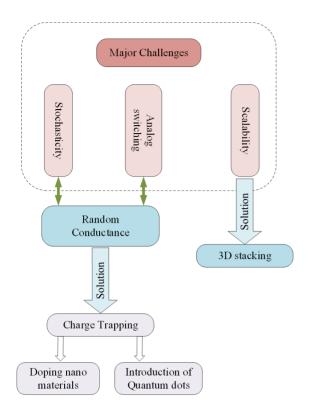

# 7. Challenges and Strategies for Memristor Integration

Typical characteristics of the memristor, such as analog switching, multilevel states, dynamic range, variation, eight updates, linearity, retention and endurance, will influence the performance of the neuromorphic computing system. <sup>63,83</sup> The analog switching feature will allow the memristor to be used in neuromorphic computing. Analog programming and multiplication accuracy in the crossbar array are more important in the neural network. <sup>86,87</sup> The crossbar wire can consume the input voltage and thus cause incorrect computation. And this is undesirable for memristor-based neural networks.

The synaptic strength changes in accordance with the input signal and is referred to as the linearity update of the neuron model. In addition, the programming pulse adjusts the conductivity of the memristor linearly to the synaptic memristor. Thus, the linear function of this conductance affects the efficiency of the synapses. But then, most memristor synapses show a nonlinear weight update. From now on, the nonlinear behavioral functions of memristor need to be upgraded for efficient networking architecture. On the other hand, multilevel state and dynamic ranges have an impact on storage capacity resolution due to the number of conductivity states in memristor.

Variations in the current and operating potential of the SET/RESET memristor usually occur between devices and cycles. The limitations of fabrication techniques, i.e., nonideal film morphology and homogeneity, cause dissimilar electrical functions in different memristor and therefore lead to variation.<sup>88,89</sup> In addition to such device variations, cycle variations<sup>90</sup> are usually due to random path formation in the memristor device. This stochasticity is not worthy of this kind of networking practice. On the other hand, this stochasticity is correspondingly exploited for other requests, such as the creation of random numbers for security purposes.<sup>91,92</sup> Jiang et al.<sup>93</sup> have developed a true

random number generator. Such stochasticity could also be exploited to avoid circuit disturbance.  $^{94}$  This method has been proposed and demonstrated by Al-Shedivat  $et\ al.^{65}$  Similarly, more research has been done to incorporate stochasticity into the memristor system.  $^{95-97}$

Such stochasticity concerns may also be addressed by reducing the size of the device. Random filament formation generally causes variation in memristor. Existing technology has reached a 10 nm scale in the memristor device. <sup>98</sup> The device can theoretically be further scaled down to the atomic level. <sup>99</sup> In addition to improving the uniformity of the device, scaling down the size also helps to reduce the programming current and power consumption. <sup>63,85</sup>

The preparation of CMOS compatible devices is another major challenge for memristor devices. Various types of electrodes in the manufacture of bipolar redox memristor have been reported for decent CMOS compatibility performance. Electrodes such as TiN and TaN have recently been used as a further course of action for manufacturing. Although these are not inert metals like Pt, the device fabricated with this material proves that it is compatible with the conventional system. However, modern CMOS systems need to be enhanced for the use of other metals. 101

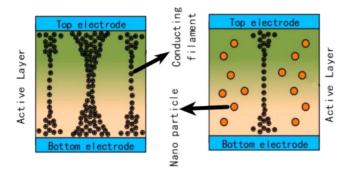

# 8. Upgradation of Memristor for Neuromorphic Computing

The typical concern about the manufacture of memristor for neuromorphic computing is the variation in stochasticity of the device. This broad variation is generally the result of random filament formation in the active layer of the device consisting of more oxygen vacancy. <sup>102</sup> If the formation of the conductive filament is controlled in some way, the variation of the devices can be reduced, resulting in an efficient memristor-based neural networking system. This can only be done by trapping charges in the active layer of the device (see Fig. 12).

The introduction of certain nanometals in the active layer along with active dielectric material is one way of trapping charges in the device. <sup>103</sup> Goswami *et al.* demonstrated the improved performance of the device by introducing nanometal in the dielectric material and actively using the charging trapping method to reduce the variation in the device. <sup>104</sup> Wu *et al.* introduced the Al metal in the active resistance layer to demonstrate the

Fig. 12. Random and controlled conductance formation.

multilevel resistance of the device. <sup>105</sup> But introducing this method also has some hindrances, such as the uneven distribution of nanoparticles in the active layer. This leads to an uneven distribution of the system density due to the thermal dynamic method. In order to overcome this drawback, novel quantum dot materials may be used along with dielectric active materials to achieve even distribution in the device (see Fig. 13).

Graphene is one of the attractive materials used for charge trapping material in memristor devices. Graphene quantum dot has been fabricated in oxide-based memristor for improved device performance. Wang  $et\ al.$  have shown that graphene quantum dots are an effective trapping layer of charges associated. Wang  $et\ al.$  have introduced quantum

Fig. 13. Random and controlled conductance formation.

dots of graphene oxide in memristive devices for controlling the movement of oxygen vacancy and thus the formation of filament conductors. <sup>107</sup> They achieved 63\% more efficiency in trapping oxygen vacancies by using a graphene quantum dot. Yan et al. have fabricated a lead sulphide quantum dot trapping device. <sup>108</sup> The lead sulphide quantum dots also helped to trap charges and increase the performance of the device. A number of charge trapping structures have been studied and reported for improvement of memristor devices (listed in Table 1). The device with low scan voltage and the highest trapping density of charge is best suited for neuromorphic applications. As a result, memristor can be upgraded to achieve a repeatable multilevel resistance to high density brains like a neuron network.

The 3D stacked crossbar memristor array is another key factor for using more memory and synapse than the human brain. 114 Since cognitive operation is only possible with large quantities of devices, in particular cells, it obviously requires a denser memristor device. For the integration of a high-density array per area, 3D stacked architecture is more beneficial for the design of a memristor crossbar structure. For example, SiO<sub>2</sub> material was used to demonstrate 3D memristor stacked by Li

Table 1. The summary of reported charge trapping structures.

| Reference                                                                                                    | Charge trapping layer                                                                                                                 | Charge trapped density $(cm^{-2})$                                                                                                                        | Scan voltage (V)                                                      |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Zhang et al. 109 Chen et al. 110 Joo et al. 111 Shi et al. 112 Ji et al. 113 Wang et al. 107 Wang et al. 107 | $SiO_2/HfO_2$ $SiO_2/(HfO_2/Al2O_3)_2$ $SiO_2/GQD/SiO_2$ $SiO_2/LaNbO/Al2O_3$ $GOD/PS/Pentacene$ $SiO_2/ZHO/SiO_2$ $SiO_2/GOQD/SiO_2$ | $7.50 \times 10^{12}$ $6.40 \times 10^{12}$ $2.80 \times 10_{11}$ $1.91 \times 10_{13}$ $7.20 \times 10_{12}$ $7.45 \times 10_{13}$ $1.21 \times 10_{14}$ | $\pm 10$ $\pm 12$ $\pm 10$ $\pm 12$ $\pm 12$ $\pm 12$ $\pm 5$ $\pm 5$ |

Fig. 14. Schematic diagram of 3D stacked memristor.  $^{95}$

et al.<sup>115</sup> This 3D stacking shows the typical structure that mimics the human brain like a neural network (Fig. 14).

In addition, enhanced and desirable memristor synapses have yet to be testified in the neuromorphic computing network. The synapses model can therefore be designed in accordance with individual neuromorphic networks for end-use applications. In addition, supervised learning-based networks may be used to address such variation issues.<sup>83</sup> The known error value is calculated to change the synapses in the supervised learning network. Conversely, unsupervised learning networks directly affect the variation of unknown target values. 117-119 During the learning process, memristor synapses are updated repeatedly to achieve final conductance. As a result, large endurance cycles and retention time are encouraging to realize the desired performance of memristor-based neuromorphic networks. Cytomorphic engineering is also trying to research biological systems' cellular activity through electronics. 120 Two-terminal devices can capture the nonlinear and stochastic activity of biochemical reactions. Hanna et al. present the design of several building blocks based on analogue memory circuits that essentially model the biophysical mechanisms of gene expression. 120 This method can provide a quick and easy emulative framework for the analysis of genetic circuits and arbitrary large-scale biological networks in systems and synthetic biology.

#### 9. Conclusion

Every year, the need for alternative computing systems is changing. However, non-von Neumann systems with massive parallel calculations by consuming low power can learn online and perform in real time. Memristor-based neural network circuits will be considered a competitive hardware candidate in alternative computer architectures. We discussed

the emerging memory instrument that can be used to overcome the battle neck of von Neumann's architecture in the bioneural computing system. A number of challenges will be faced strategically in the immediate future, despite great successes. This paper also addresses the main obstacles in combining memristor and neuromorphic architecture, and how these difficulties can be overcome.

System instability and uncertainty have been described as current problems for most memory-based applications. This is the opposite of the biological process. Despite noise, nonlinearity, variability and volatility, biological systems work well. It is still unclear, however, that the effectiveness of biological systems actually depends on these obstacles. Neural modeling is sometimes avoided because it is not easy to model and study. The possibility of exploiting these properties is therefore, of course, a critical path to success in the achievement of artificial and biological systems.

### Acknowledgments

This work is supported by the Key project's funding of NSFC (No. 61836010) and the fundings of National Key Research and Development Program of China (No. 2019YFB2204600, No. 2019YFB2205001 and No. 2019YFB2205005).

#### References

- Y. Chen, H. Li, C. Wu, C. Song, S. Li, C. Min, H.-P. Cheng, W. Wen and X. Liu, *Integ. VLSI J.* 61, 49 (2018), https://doi.org/10.1016/j.vlsi.2017. 11.001.

- 2. P. Chi, S. Li, C. Xu, T. Zhang, J. Zhao, Y. Liu, Y. Wang, and Y. Xie, PRIME: A novel processing-in-memory architecture for neural network computation in ReRAM-based main memory, in ACM/IEEE 43rd Annual International Symposium on Computer Architecture (ISCA) (2016), pp. 27-39, https://dl.acm.org/doi/10.1145/3007787.3001140.

- 3. C. Mead, Analog VLSI and neural system, NASA STI/Recon Technical Report A (1989).

- N. K. Upadhyay, S. Joshi and J. J. Yang, Sci. China Inf. Sci. 59, 061404 (2016), https://doi.org/ 10.1007/s11432-016-5565-1.

- R. S. Williams, IEEE Spectr. 45, 28 (2008), https://doi.org/10.1109/MSPEC.2008.4687366.

- Q. Xia, W. Robinett, M. W. Cumbie, N. Banerjee, T. J. Cardinali, J. J. Yang, W. Wu, X. Li, W. M. Tong, D. B. Strukov, G. S. Snider, G. Medeiros-Ribeiro and R. S. Williams, *Nano Lett.* 9, 3640 (2009).

- S. Pi, P. Lin and Q. Xia, Vac. Sci. Technol. B: Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 31, 06FA02 (2013), https://doi.org/ 10.1116/1.4827021.

- S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder and W. Lu, *Nano Lett.* 10, 1297 (2010), https://doi.org/10.1021/nl904092h.

- M. D. Pickett and R. S. Williams, Nanotechnology 23, 215202 (2012), https://doi.org/10.1088/0957-4484/23/21/215202.

- L. O. Chua, *IEEE Trans. Circuit Theory* 18, 507–519 (1971), https://doi.org/10.1109/TCT. 1971.1083337.

- D. B. Strukov, G. S. Sinder, D. R. Stewart and R. S. Williams, *Nature* 453, 80 (2008), https://doi.org/10.1038/nature06932.

- H. Mostafa, A. Khiat, A. Serb, C. G. Mayr, G. Indiveri and T. Prodromakis, Front. Neurosci.

9, 1 (2015), https://doi.org/10.3389/fnins.2015. 00357.

- J. Yang, M. D. Pickett, X. Li, D. A. A. Ohlberg, D. R. Atewart and R. S. Williams, Nat. Nanotechnol. 3, 429 (2008), https://doi.org/ 10.1038/nnano.2008.160.

- 14. L. Wu, C. Dong, X. Wang, J. Li and M. Li, *J. Alloys Compd.* **779**, 794 (2019), https://doi.org/10.1016/j.jallcom.2018.11.345.

- G. Ma, X. Tang, H. Su, Y. Li, H. Zhang and Z. Zhong, *IEEE Trans. Electron Devices* 61, 1237 (2014), https://doi.org/10.1109/TED. 2014.2309975.

- 16. W. G. Kim, J. Y. Kim, J. W. Moon, M. S. Joo, H. J. Choi, S. G. Kim, K. J. Lee, K. Hong, S. K. Park, Effect of Inserting Al2O3 Layer and Device Structure in HfO2-Based ReRAM for Low Power Operation, in 2012 4th IEEE International Memory Workshop, Milan, 2012, pp. 1–4, https://doi.org/10.1109/IMW.2012.6213681.

- M. Kim and K. C. Choi, *IEEE Trans. Electron Devices* 64, 3508 (2017), https://doi.org/10.1109/ TED.2017.2716831.

- S.-H. Liu, W.-L. Yang, C.-C. Wu, T.-S. Chao, M.-R. Ye, Y.-Y. Su, P.-Y. Wang and M.-J. Tsai, *IEEE Electron Device Lett.* 34, 123 (2013), https://doi.org/10.1109/LED.2012.2224633.

- M. Wang, S. Cai, C. Pan, C. Wang, X. Lian, Y. Zhuo, K. Xu, T. Cao, X. Pan, B. Wang, S.-J. Liang, J. J. Yang, P. Wang and F. Miao, *Nat. Electron.* 1, 203 (2018), https://doi.org/10.1038/s41928-018-0021-4.

- 20. S. Zou, P. Xu and M. Hamilton, *Electron. Lett.* 4, 829 (2013), https://doi.org/10.1049/el.2013.1302.

- V. Garcia, S. Fusil, K. Bouzehouane, S. Enouz-Vedrenne, N. Mathur, A. Barthélémy and M. Bibes, *Nature* 460, 81 (2009), https://doi.org/10.1038/nature08128.

- P. Krzysteczko, J. Münchenberger, M. Schäfers, G. Reiss and A. Thomas, Adv. Mater. 24, 762 (2012), https://doi.org/10.1002/adma.201103723.

- X. Zhou, L. Wu, Z. Song, F. Rao, K. Ren, C. Peng, S. Song, B. Liu, L. Xu and S. Feng, Appl. Phys. Lett. 103, 072114 (2013), https://doi.org/10.1063/1.4818662.

- D. Apalkov, A. Ong, A. Driskill-Smith, M. Krounbi, A. Khvalkovskiy, S. Watts, V. Nikitin, X. Tang, D. Lottis, K. Moon, X. Luo and E. Chen, ACM J. Emerg. Technol. Comput. Syst. 9, 1 (2013), https://doi.org/10.1145/2463585. 2463589.

- 25. I. Valov, *ChemElectroChem* 1, 26 (2013), https://doi.org/10.1002/celc.201300165.

- K. Szot, W. Speier, G. Bihlmayer and R. Waser, Nat. Mater. 5, 312 (2006), https://doi.org/10.1038/nmat1614.

- K. Terabe, T. Hasegawa, T. Nakayama and M. Aono, *Nature* 433, 47 (2005), https://doi.org/10.1038/nature03190.

- 28. X. Zhu, J. Lee and W. Lu, *Adv. Mater.* **29**, (2017), https://doi.org/10.1002/adma.201700527.

- S. Kim, B. Choi, M. Lim, J. Yoon, J. Lee, H. Kim and S. Choi, ACS Nano 11, 2814 (2017), https://doi.org/10.1021/acsnano.6b07894.

- K. Gan, W. Chang, P. Liu and S. Sze, Appl. Phys. Lett. 115, 143501 (2019), https://doi.org/10.1063/ 1.5116359.

- 31. R. Waser, R. Dittmann, G. Staikov and K. Szot, *Adv. Mater.* **21**, 2632 (2009), https://doi.org/10.1002/adma.200900375.

- 32. M. Lübben, P. Karakolis, V. Ioannou-Sougleridis, P. Normand, P. Dimitrakis and I. Valov, *Adv. Mater.* **27**, 6202 (2015), https://doi.org/10.1002/adma.201502574.

- 33. F. Zhuge, K. Li, B. Fu, H. Zhang, J. Li, H. Chen, L. Liang, J. Gao, H. Cao, Z. Liu and H. Luo, AIP Adv. 5, 057125 (2015), https://doi.org/10.1063/1.4921089.

- 34. X. Yan, J. Zhao, S. Liu, Z. Zhou, Q. Liu, J. Chen and X. Liu, *Adv. Funct. Mater.* **28**, 1705320 (2018), https://doi.org/10.1002/adfm.201705320.

- 35. S. Zhang, S. Luo, N. Xu, Q. Zou, M. Song, J. Yun, Q. Luo, Z. Guo, R. Li, W. Tian, X. Li, H. Zhou, H. Chen, Y. Zhang, X. Yang, W. Jiang, K. Shen, J. Hong, Z. Yuan, L. Xi, K. Xia, S. Salahuddin, B. Dieny and L. You, Adv. Electron. Mater. 5, 1970022 (2019), https://doi.org/10.1002/aelm.201800782.

- E. Dagotto, T. Hotta and A. Moreo, *Phys. Rep.* 344, 1 (2001), https://doi.org/10.1016/S0370-1573(00)00121-6.

- 37. Y. Chen and X. Wang, Compact modeling and corner analysis of spintronic memristor, 2009 IEEE/ACM Int. Symp. Nanoscale Architectures

- (2009)), pp. 7–12, https://doi.org/10.1109/NANOARCH.2009.5226363.

- M. Wu, C. Yang, D. Shi, R. Wang, L. Xu, H. Xiao and K. Baerner, AIP Advances 4, 047123 (2014), https://doi.org/10.1063/1.4872216.

- S. Parkin, M. Hayashi and L. Thomas, Science

320, 190 (2008), https://doi.org/10.1126/science.

1145799.

- D. Ielmini and A. Lacaita, Mater. Today 14, 600 (2011), https://doi.org/10.1016/S1369-7021 (11)70301-7.

- X. Zhou, M. Xia, F. Rao, L. Wu, X. Li, Z. Song, S. Feng and H. Sun, ACS Appl. Mater. Interfaces 6, 14207 (2014), https://doi.org/10.1021/am503502q.

- W. Zhang, R. Mazzarello, M. Wuttig and E. Ma, Nat. Rev. Mater. 4, 150 (2019), https://doi.org/ 10.1038/s41578-018-0076-x.

- Y. Li, Z. Wang, R. Midya, Q. Xia and J. Yang, J. Phys. D: Appl. Phys. 51, 503002 (2018), https://doi.org/10.1088/1361-6463/aade3f.

- J. Lappalainen, J. Mizsei and M. Huotari, J. Appl. Phys. 125, 044501 (2019), https://doi.org/10.1063/1.5037990.

- A. Chanthbouala, V. Garcia, R. O. Cherifi, K. Bouzehouane, S. Fusil, X. Moya, S. Xavier, H. Yamada, C. Deranlot, N. D. Mathur, M. Bibes, A. Barthélémy and J. Grollier, *Nat. Mater.* 11, 860 (2012), https://doi.org/10.1038/nmat3415.

- D. J. Kim, H. Lu, S. Ryu, C.-W. Bark, C.-B. Eom, E. Y. Tsymbal and A. Gruverman, *Nano Lett.* 12, 5697 (2012), https://doi.org/10.1063/1.4823989.

- M. Prezioso, F. Merrikh-Bayat, B. D. Hoskins, G. C. Adam, K. K. Likharev and D. B. Strukov, Nature 521, 61 (2015), https://doi.org/10.1038/ nature14441.

- 48. Z. Wang, S. Joshi, S. Savel'ev, W. Song, R. Midya, Y. Li, M. Rao, P. Yan, S. Asapu, Y. Zhuo, H. Jiang, P. Lin, C. Li, J. H. Yoon, N. K. Upadhyay, J. Zhang, M. Hu, J. P. Strachan, M. Barnell, Q. Wu, H. Wu, R. S. Williams, Q. Xia and J. Yang, Nat. Electron. 1, 137 (2018), https://doi.org/10.1038/s41928-018-0023-2.

- 49. D. Poole, A. Mackworth and R. Goebel, *Computational Intelligence: A Logical Approach* (Oxford University Press, New York, 1998).

- A. Sally, Reflections on the memory wall, Conf. Computing Frontiers, Italy, 14–16 April (ACM, New York, 2004), p. 162.

- 51. C. Mead, Proc. IEEE 78, 1629 (1990).

- M. Versace and B. Chandler, *IEEE Spectr.* 47, 30 (2010), https://doi.org/10.1109/MSPEC.2010. 5644776.

- S. Selvaluxmiy, T. N. Kumara, P. Keerthanan,

R. Velmakivan, R. Ragel and S. Deegalla,

IEEE Int. Conf. Information and Automation for

- Sustainability (ICIAfS), Galle, Sri Lanka, 16–19 December (2016), pp. 1–6.

- T. Tuma, A. Pantazi, M. Le Gallo, A. Sebastian and E. Eleftheriou, *Nat. Nanotechnol.* 11, 693 (2016), https://doi.org/10.1038/nnano.2016.70.

- A. E. Pereda, Nat. Rev. Neurosci. 15, 250 (2014), https://doi.org/10.1038/nrn3708.

- M. Prezioso, F. Merrikh Bayat, B. Hoskins, K. Likharev and D. Strukov, *Nature* 521, 61 (2015), https://doi.org/10.1038/nature14441.

- 57. S. Yu (ed.), Neuro-Inspired Computing Using Resistive Synaptic Devices (Springer, Gewerbestrasse, Cham, Switzerland, 2017).

- M. A. Zidan, J. P. Strachan and W. D. Lu, *Nat. Electron.* 1, 22 (2018), https://doi.org/10.1038/s41928-017-0006-8.

- 59. H. Markram, *Nat. Rev. Neurosci.* **7**, 153 (2006), https://doi.org/10.1038/nrn1848.

- S. B. Furber, D. R. Lester, L. A. Plana, J. D. Garside, E. Painkras, S. Temple, A. D. Brown, *IEEE Trans. Comput.* 62, 2454 (2013), https://doi.org/10.1109/JPROC.2014.2304638.

- 61. P. A. Merolla, J. V. Arthur, R. Alvarez-Icaza, A. S. Cassidy, J. Sawada, F. Akopyan, B. L. Jackson, N. Imam, C. Guo, Y. Nakamura, B. Brezzo, I. Vo, S. K. Esser, R. Appuswamy, B. Taba, A. Amir, M. D. Flickner, W. P. Risk, R. Manohar and D. S. Modha, Science 345, 668 (2014), https://doi.org/10.1126/science.1254642.

- 62. G. W. Burr, R. M. Shelby, S. Sidler, C. di Nolfo, J. Jang, I. Boybat, R. S. Shenoy, P. Narayanan, K. Virwani, E. U. Giacometti, B. N. Kurdi and H. Hwang, *IEEE Trans. Electron Dev.* 62, 3498 (2015), https://doi.org/10.1109/IEDM.2014. 7047135.

- J. J. Yang, D. B. Strukov and D. R. Stewart, *Nat. Nanotechnol.* 8, 13 (2013), https://doi.org/ 10.1038/nnano.2012.240.

- S. La Barbera, D. Vuillaume and F. Alibart, ACS Nano 9, 941 (2015), https://doi.org/10.1021/ nn506735m.

- 65. M. Al-Shedivat, R. Naous, G. Cauwenberghs and K. Salama, *IEEE J. Emerg. Sel. Top. Circuits Syst.* **5**, 242 (2015), https://doi.org/10.1109/JETCAS.2015.2435512.

- R. Yang, H. Huang, Q. Hong, X. Yin, Z. Tan, T. Shi, Y. Zhou, X. Miao, X. Wang, S. Mi, C. Jia and X. Guo, Adv. Funct. Mater. 28, 1704455 (2017), https://doi.org/10.1002/adfm.201704455.

- S. Park, J. Noh, M. Choo, A. Sheri, M. Chang,

Y. Kim, C. Kim, M. Jeon, B. Lee, B. Lee and

H. Hwang, *Nanotechnology* 24, 384009 (2013),

https://doi.org/10.1088/0957-4484/24/38/384009.

- T. Tuma, A. Pantazi, M. Le Gallo, A. Sebastian and E. Eleftheriou, *Nat. Nanotechnol.* 11, 693 (2016), https://doi.org/10.1038/nnano.2016.70.

- 69. M. Teimoori, A. Ahmadi, S. Alirezaee, S. V. Al-Din Makki and M. Ahmadi, A novel memristor based integrate-and-fire neuron implementation using material implication logic, *IEEE 28th Cana*dian Conf. Electrical and Computer Engineering (CCECE), Halifax, NS, 3–6 May (IEEE, 2015), pp. 1176–1179.

- A. Mehonic and A. Kenyon, Front. Neurosci.

10, 57 (2016), https://doi.org/10.3389/fnins.2016. 00057.

- 71. N. Hou, F. He, Y. Zhou, Y. Chen and X. Yan, *IEEE Access* **6**, 883 (2017), https://10.1109/ACCESS.2017.2776295.

- F. M. Bayat, X. Guo, M. Klachko, M. Prezioso,

K. K. Likharev and D. B. Strukov, *IEEE Trans. Neural Netw. Learn. Syst.* 29, 4782–4790 (2018),

https://doi.org/10.1109/TNNLS.2017.2778940.

- M. Al-Shedivat, R. Naous, G. Cauwenberghs and K. Salama, *IEEE J. Emerg. Sel. Top. Circuits* Syst. 5, 242 (2015), https://doi.org/10.1109/JET-CAS.2015.2435512.

- J. Shamsi, A. Amirsoleimani, S. Mirzakuchaki and M. Ahmadi, *Neural Comput. Appl.* 28, 1 (2017), https://doi.org/10.1007/s00521-015-2047-0.

- A. Pantazi, S. Woźniak, T. Tuma and E. Eleftheriou, Nanotechnology 27, 355205 (2016), https://doi.org/10.1088/0957-4484/27/35/355205.

- S. Kim, B. Choi, M. Lim, J. Yoon, J. Lee, H. D. Kim and S. J. Choi, ACS Nano 11, 2814 (2017), https://doi.org/10.1021/acsnano.6b07894.

- D. S. Jeong, K. M. Kim, S. Kim, B. J. Choi and C. S. Hwang, *Adv. Electron. Mater.* 2, 1600090 (2016), https://doi.org/10.1002/aelm.201670051.

- R. Ranjan, P. M. Ponce, W. L. Hellweg, A. Kyrmanidis, L. Abu Saleh, D. Schroeder and W. H. Krautschneider, J. Circuits Syst. Comput. 26, 1750183 (2017), http://dx.doi.org/10.1142/S0218126617501833.

- B. Qu, H. W. Du, T. Wan, X. Lin, A. Younis and D. W. Chu, *Mater. Des.* 129, 173 (2017), https://doi.org/10.1016/j.matdes.2017.05.022.

- 80. W. R. Cai, F. Ellinger and R. Tetzlaff, *IEEE Trans. Biomed. Circuits Syst.* **9**, 87 (2015), https://doi.org/10.1109/TBCAS.2014.2318012.

- T. Kohonen, Self-organization and Associative Memory, Springer Series in Information Sciences, Vol. 8 (Springer, Berlin/Heidelberg, Germany, 1989).

- 82. K. Steinbuch, *Kybernetik* 1, 36–45 (1961), https://doi.org/10.1007/BF00293853 (in German).

- S. Choi, S. Jang, J.-H. Moon, J. C. Kim, H. Y. Jeong, P. Jang, K.-J. Lee and G. Wang, NPG Asia Mater. 10, 1097 (2018), https://doi.org/10.1038/s41427-018-0101-y.

- 84. W. Huh, S. Jang, J. Y. Lee, D. Lee, J. M. Lee, H.-G. Park, J. C. Kim, H. Y. Jeong, G. Wang

- and C.-H. Lee, *Adv. Mater.* **30**, 1801447 (2018), https://doi.org/10.1002/adma.201801447.

- S. Ham, S. Choi, H. Cho, S. I. Na and G. Wang, Adv. Funct. Mater. 29, 1806646 (2019).

- C. H. Bennett, D. Querlioz and J.-O. Klein, *IEEE/ACM Int. Symp. Nanoscale Architectures*  (NANOARCH), Newport, RI, 25–26 July (2017), pp. 125–130.

- 87. L. Chen, J. Li, Y. Chen, Q. Deng, J. Shen, X. Liang and L. Jiang, Accelerator-friendly neural-network training: Learning variations and defects in RRAM crossbar, in *Design*, Automation & Test in Europe Conf. & Exhibition (DATE), Lausanne, Switzerland, 27–31 March (2017), pp. 19–24, https://doi.org/10.23919/DATE.2017. 7926952.

- S. Gaba, P. Knag, Z. Zhang and W. Lu, Memristive devices for stochastic computing, in *IEEE Int. Symp. Circuits and System (ISCAS)*, Melbourne, VIC, 1–5 June (2014), pp. 1–5, https://doi.org/10.1109/ISCAS.2014.6865703.

- 89. A. Chen and M. Lin, Variability of resistive switching memories and its impact on crossbar array performance, *Int. Reliability Physics Symp.*, Monterey, CA, 10–14 April (2011), pp. 7.1–7.4, https://doi.org/10.1109/IRPS.2011.5784590.

- 90. S. Yu, X. Guan and H.-S. Philip Wong, *IEEE Trans. Electron Devices* **59**, 1183 (2012), https://doi.org/10.1109/TED.2012.2184544.

- 91. T. Zhang, M. Yin, C. Xu, X. Lu, X. Sun, Y. Yang and R. Huang, *Nanotechnology* **28**, 455202 (2017), https://doi.org/10.1088/1361-6528/aa8b3a.

- 92. P. Koeberl, U. Kocabas and A.-R. Sadeghi, Memristor PUFs: A new generation of memory-based physically unclonable function, in *Design*, Automation & Test in Europe Conf. & Exhibition, Grenoble, France, 18–22 March (2013), pp. 428–431, https://doi.org/10.7873/DATE.2013.096.

- H. Jiang, D. Belkin, S. E. Savel'ev, S. Lin, Z. Wang, Y. Li, S. Joshi, R. Midya, C. Li, M. Rao, M. Barnell, Q. Wu, J. J. Yang and Q. Xia, *Nat. Commun.* 8, 1 (2017), https://doi.org/10.1038/s41467-017-00869-x.

- 94. W. Woods, J. Burger and C. Teuscher, Synaptic weight states in a locally competitive algorithm for neuromorphic memristive hardware, *IEEE/ACM Int. Symp. Nanoscale Architectures (NANO-ARCH)*, Paris, France, 8–10 July (2014), pp. 19–24, http://dx.doi.org/10.1109/TNANO.2015.2449835.

- 95. J. Lin and J. S. Yuan, Capacitor-less RRAM-based stochastic neuron for event-based unsupervised learning, *IEEE Biomedical Circuits and Systems Conf.* (BioCAS), Torino, Italy, 19–21 October (2017), https://doi.org/ 10.1109/BIOCAS.2017.8325169.

- R. Naous, M. Al Shedivat, E. Neftci, G. Cauwenberghs and K. N. Salama, AIP Adv. 6, 111304 (2016), https://doi.org/10.1063/1.4967352.

- M. Suri, V. Parmar, A. Kumar, D. Querlioz and F. Alibart, 15th Non-Volatile Memory Technology Symp. (NVMTS), Beijing, China, 12–14 October (2015)), https://doi.org/10.1109/ NVMTS.2015.7457484

- 98. B. Govoreanu, A. Redolfi, L. Zhang, C. Adelmann, M. Popovici, S. Clima, H. Hody, V. Paraschiv, I. P. Radu, A. Franquet, J.-C. Liu, J. Swerts, O. Richard, H. Bender, L. Altimime and M. Jurczak, Vacancy-modulated conductive oxide resistive RAM (VMCO-RRAM): An area-scalable switching current, self-compliant, highly nonlinear and wide on/off-window resistive switching cell, *IEEE Int. Electron Devices Meeting*, Washington, DC, 9–11 December (2013), pp. 10.2.1–10.2.4, https://doi.org/10.1109/IEDM.2013.6724599.

- Y.-E. Syu, T.-C. Chang, J.-H. Lou, T.-M. Tsai, K.-C. Chang, M.-J. Tsai, Y.-L. Wang, M. Liu and S. M. Sze, *Appl. Phys. Lett.* 102, 172903 (2013), https://doi.org/10.1063/1.4802821.

- 100. M. Jo, R. Katsumura, A. Tsurumaki-Fukuchi, M. Arita, Y. Takahashi, H. Ando and T. Morie, Analog Memory Characteristics of 1T1R MoOx Resistive Random Access Memory, *IEEE Silicon Nanoelectronics Workshop (SNW)*, Honolulu, HI, 12–13 June (2016), pp. 78–79, https://doi.org/ 10.1109/SNW.2016.7577993.

- V. Y. Q. Zhuo, M. Li, Y. Guo, W. Wang, Y. Yang,

Y. Jiang and J. Robertson, J. Appl. Phys. 120,

024504 (2016), https://doi.org/10.1063/1.4955044.

- 102. S. B. Lee, S. C. Chae, S. H. Chang and T. W. Noh, Appl. Phys. Lett. 94, 173504 (2009), https://doi.org/10.1063/1.3126019.

- S. K. Vishwanath and J. Kim, J. Mater. Chem. C 4, 10967 (2016), https://doi.org/10.1039/ C6TC03607D.

- 104. S. Goswami, A. J. Matula, S. P. Rath, S. Hedström, S. Saha, M. Annamalai, D. Sengupta, A. Patra, S. Ghosh, H. Jani, S. Sarkar, M. R. Motapothula, C. A. Nijhuis, J. Martin, S. Goswami, V. S. Batista and T. Venkatesan, *Nat. Mater.* 16, 1216 (2017), https://doi.org/10.1038/nmat5009.

- 105. L. Wu, H. Liu, J. Li, S. Wang and X. Wang, Nanoscale Res. Lett. 14, 177 (2019), https:// doi.org/10.1186/s11671-019-3015-x.

- 106. C. Wang, W. He, Y. Tong, Y. Zhang, K. Huang, L. Song, S. Zhong, R. Ganeshkumar and R. Zhao, Small 13, 1603435 (2017), https://doi.org/ 10.1002/smll.201770110.

- 107. H. Wang, X. Yan, X. Jia, Z. Zhang, C.-H. Ho, C. Lu, Y. Zhang, T. Yang, J. Zhao, Z. Zhou, M. Zhao and D. Ren, IEEE J. Electron. Devices Soc.

- **6**, 464 (2018), https://doi.org/10.1109/JEDS.2018. 2820125.

- 108. X. Yan, Y. Pei, H. Chen, J. Zhao, Z. Zhou, H. Wang, L. Zhang, J. Wang, X. Li, C. Qin, G. Wang, Z. Xiao, Q. Zhao, K. Wang, H. Li, D. Ren, Q. Liu, H. Zhou, J. Chen and P. Zhou, Adv. Mater. 31, e1805284 (2019), https://doi.org/10.1002/adma.201805284.

- 109. Y. Zhang, Y. Y. Shao, X. B. Lu, M. Zeng, Z. Zhang, X. S. Gao, X. J. Zhang, J.-M. Liu and J. Y. Dai, Appl. Phys. Lett. 105, 172902 (2014), https://doi.org/10.1063/1.4900745.

- W. Chen, W.-J. Liu, M. Zhang, S.-J. Ding, D. W. Zhang and M.-F. Li, *Appl. Phys. Lett.* 91, 22908 (2007), https://doi.org/10.1063/1.2756849.

- S. S. Joo, J. Kim, S. S. Kang, S. Kim, S.-H. Choi and S. W. Hwang, Nanotechnology 25, 255203 (2014), https://doi.org/10.1088/0957-4484/25/25/255203.

- R. Shi, X. D. Huang, C. H. Leung, J. K. O. Sin and P. T. Lai, *IEEE Trans. Device Mater. Rel.* 15, 123 (2015).

- 113. Y. Ji, J. Kim, A.-N. Cha, S.-A. Lee, M. W. Lee, J. S. Suh, S. Bae, B. J. Moon, S. H. Lee, D. S. Lee, G. Wang and T.-W. Kim, *Nanotechnology* 27, 145204 (2016), https://doi.org/10.1088/0957-4484/27/14/145204.

- 114. G. C. Adam, B. D. Hoskins, M. Prezioso, F. Merrikh-Bayat, B. Chakrabarti and D. B. Strukov, *IEEE Trans. Electron. Devices* **64**, 312 (2016), https://doi.org/10.1109/TED.2016.2630925.

- C. Li, L. Han, H. Jiang, M.-H. Jang, P. Lin, Q. Wu, M. Barnell, J. J. Yang, H. L. Xin and Q. Xia, Nat. Commun. 8, 15666 (2017), https://doi.org/10.1038/ncomms15666.

- S. Vadivelmurugan, Reliable high density stacked memristor memory designs, Future Technologies Conference (FTC) 2017, Vancouver, Canada, 29– 30 November (2017)), https://saiconference.com/ Downloads/FTC2017/Proceedings/123\_Paper\_480-Reliable\_High\_Density\_Stacked\_Memristor\_Memory\_Designs.pdf.

- S. Choi, J. H. Shin, J. Lee, P. Sheridan and D. L. Wei, *Nano Lett.* 17, 3113 (2017), https://doi.org/10.1021/acs.nanolett.7b00552.

- A. Serb, J. Bill, A. Khiat, R. Berdan, R. Legenstein and T. Prodromakis, Nat. Commun.

7, 12611 (2016), https://doi.org/10.1038/ncomms-12611.

- Y. Jeong, J. Lee, J. Moon, J. H. Shin and W. D. Lu, *Nano Lett.* 18, 4447 (2018), https://doi.org/10.1021/acs.nanolett.8b01526.

- H. Hanna, L. Danial, S. Kvatinsky and R. Daniel, *IEEE Trans. Biomed. Circuits Syst.* 14, 386 (2020), https://doi.org/10.1109/tbcas.2020.2966634.